Total

Search

1. 처리장치의 개요

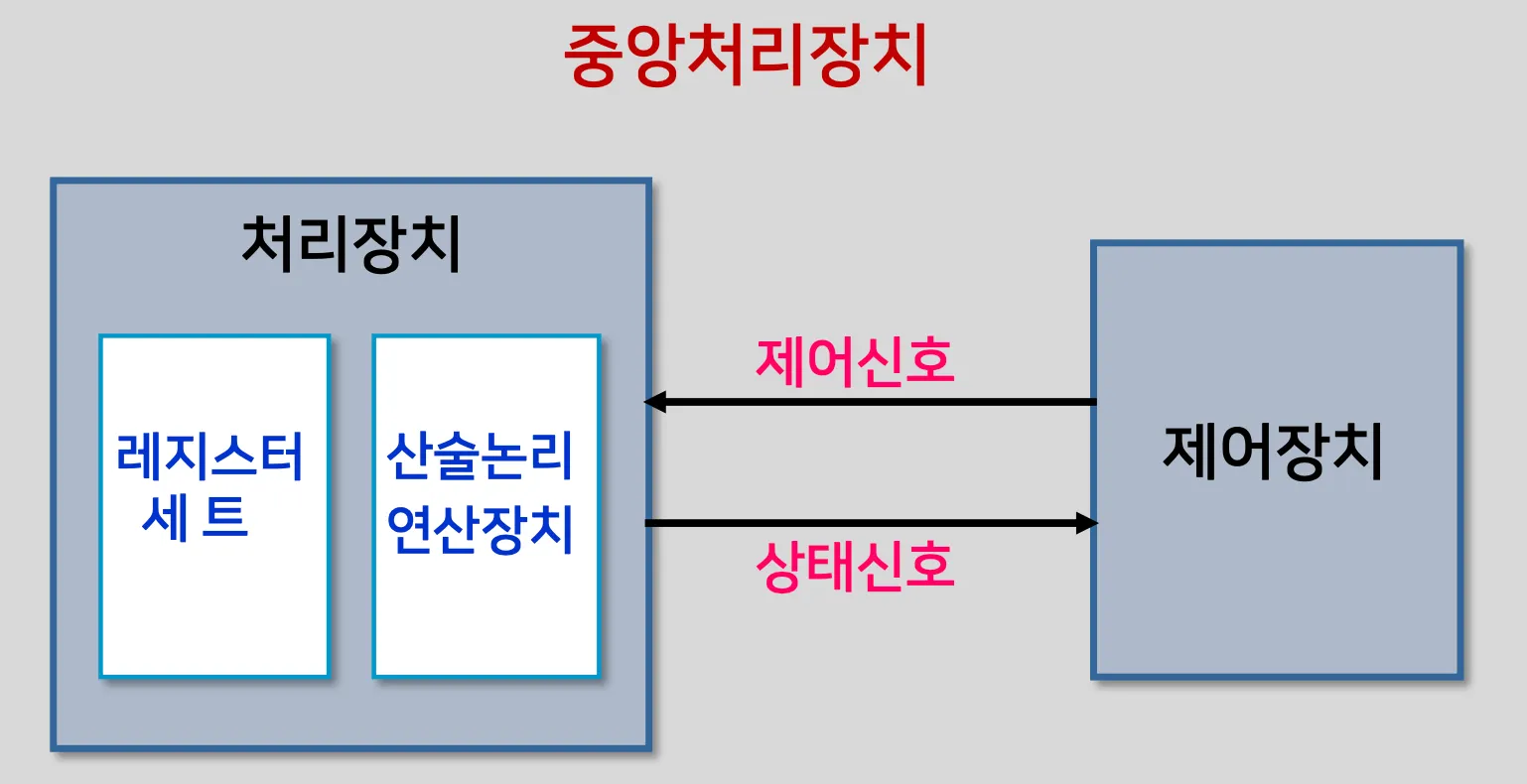

1.1. 중앙처리장치

•

중앙처리장치

◦

CPU: Central Processing Unit

•

처리 장치와 제어장치가 결합된 형태

◦

처리장치 - 데이터를 처리하는 연산 실행

◦

제어장치 - 연산의 실행순서를 결정

•

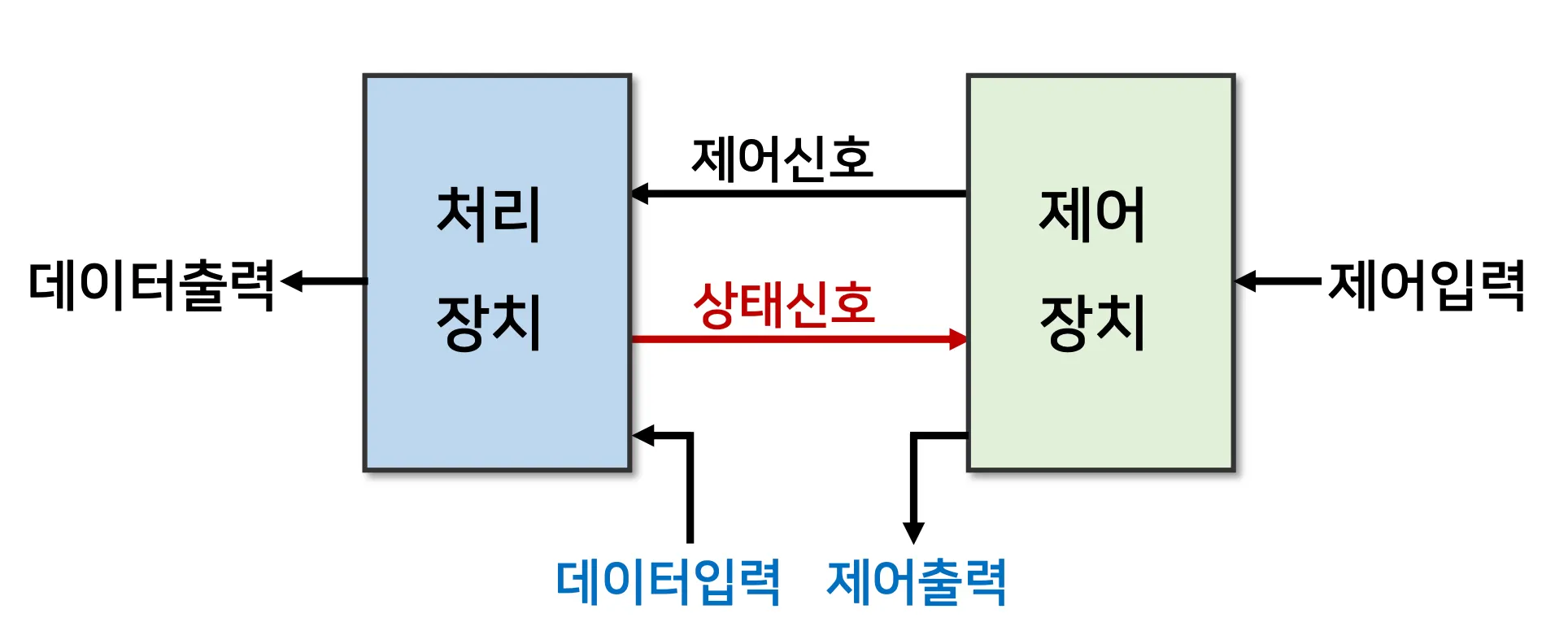

처리장치와 제어장치의 관계

1.2. 처리장치의 구성

•

산술논리연산장치와 레지스터들로 구성

◦

산술논리연산장치 (ALU: Arithmetic and LogicUnit)

▪

산술,논리,비트연산 등의 연산을 수행

◦

레지스터(Register)

▪

연산에 사용되는 데이터나 연산의 결과를 저장

▪

RAM 보다 속도가 빠름. 빠른 성능을 위해 CPU 내 데이터 저장

•

산술논리연산장치(ALU)는 독립적으로 데이터를 처리하지 못하며, 반드시 레지스터들과 조합하여 데이터를 처리

2. 마이크로 연산

2.1. 마이크로 연산

•

레지스터에 저장되어 있는 데이터에 대해 이루어지는 기본적인 연산

◦

한 레지스터의 내용을 다른 레지스터로 옮기는 것

◦

두 레지스터의 내용을 합하는 것

◦

레지스터의 내용을 1만큼 증가시키는 것 등

•

처리장치의 동작원리를 이해하기 위해서는 마이크로 연산을 이해해야 함

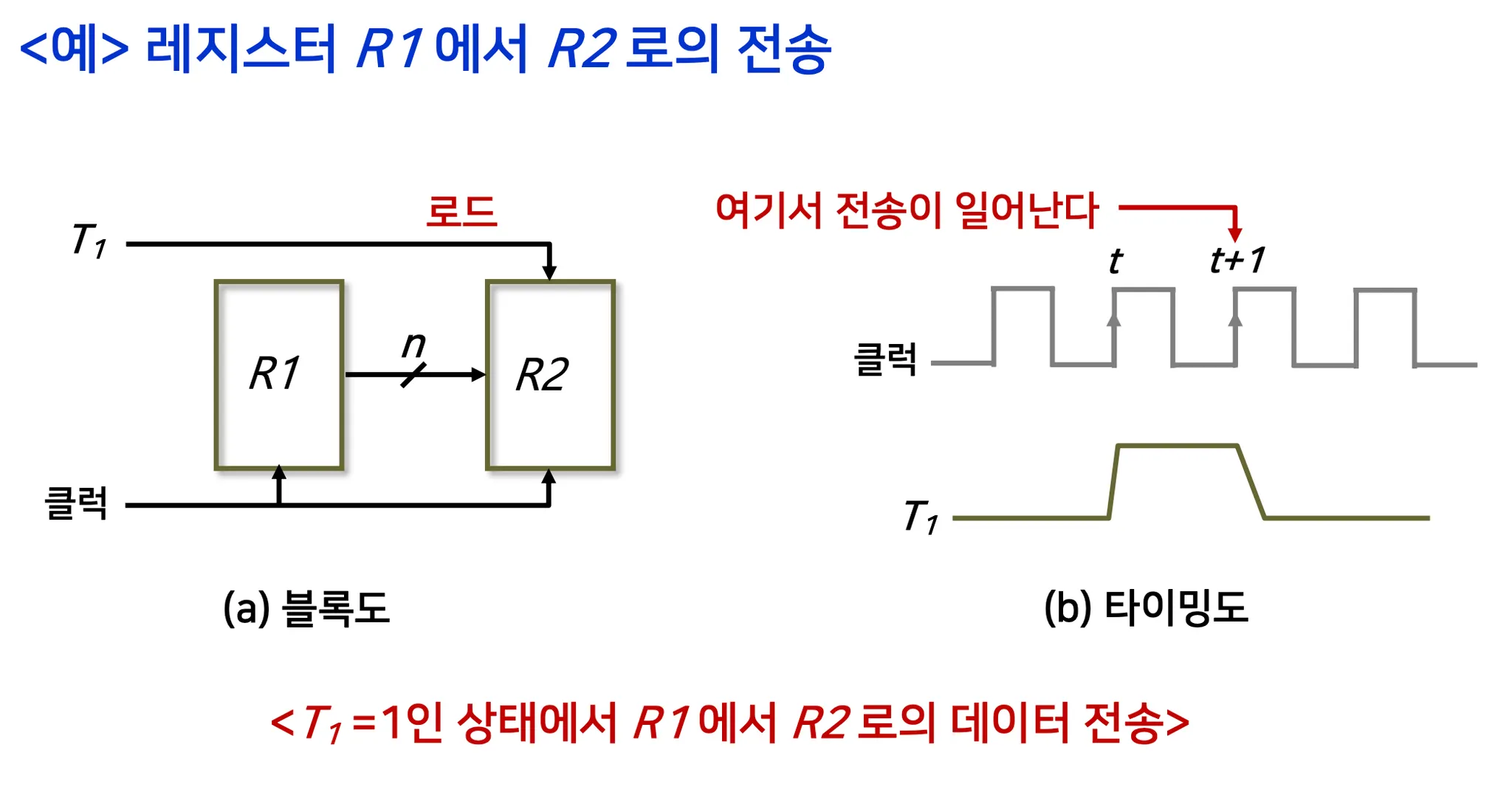

2.2. 레지스터 전송 마이크로 연산

•

레지스터 전송 마이크로 연산 (register transfer micro-operation)

•

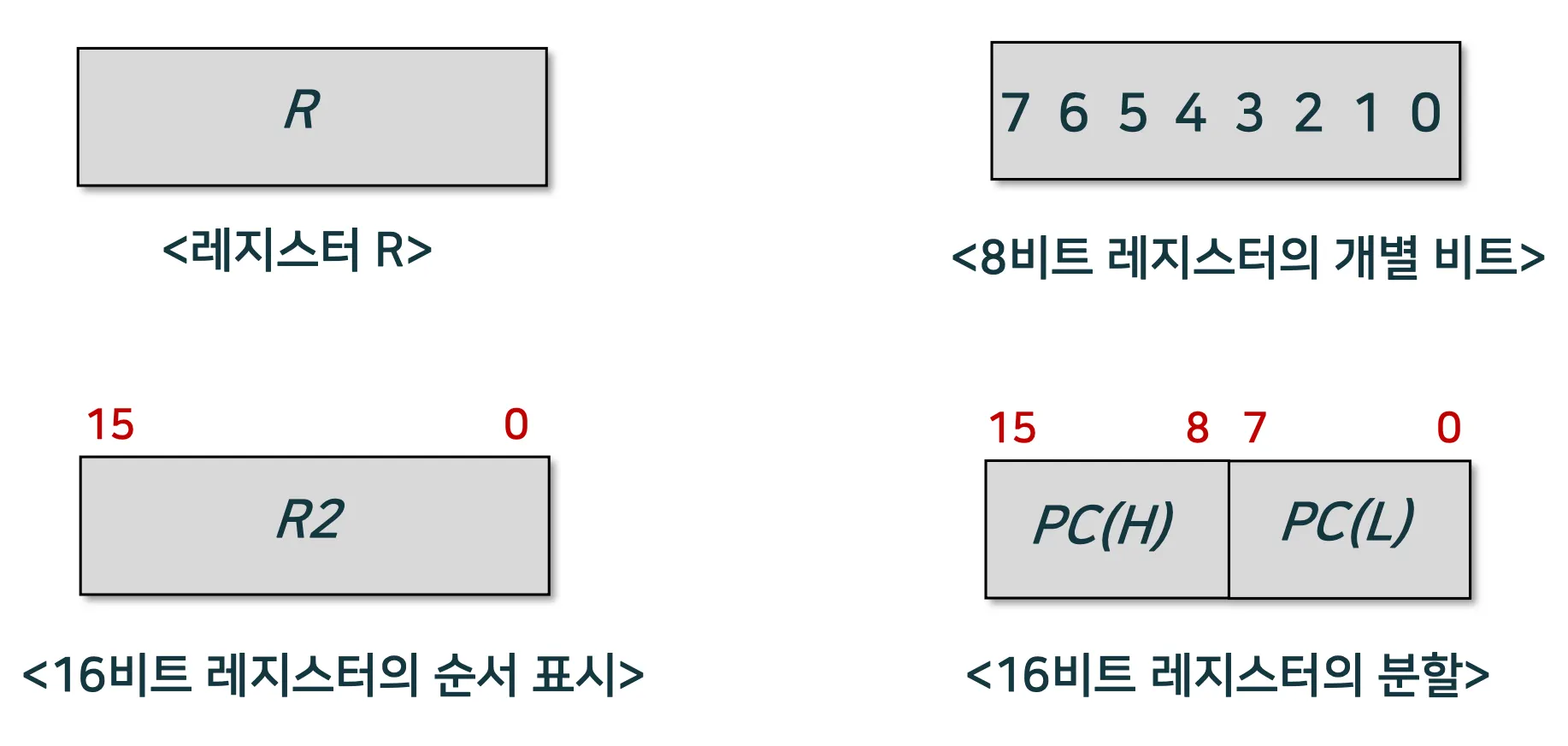

레지스터의 표현

•

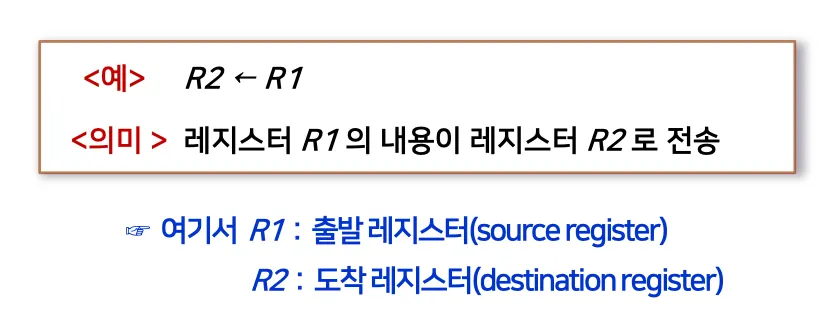

레지스터 전송 마이크로 연산

◦

한 레지스터에서 다른 레지스터로 2진 데이터를 전송하는 연산

▪

레지스터 사이의 데이터 전송은 연산자 ‘←’ 로표시

•

하드웨어적인 측면에서의 레지스터 전송

•

레지스터 전송문

•

레지스터 전송문장에서 사용되는 기본적인 기호

2.3. 산술 마이크로 연산

•

산술 마이크로 연산 (arithmetic micro-operation)

•

레지스터 내의 데이터에 대해서 실행되는 산술연산

•

기본적인 산술 연산으로는 덧셈, 뺄셈, 1증가, 1감소, 그리고 보수연산이 있다.

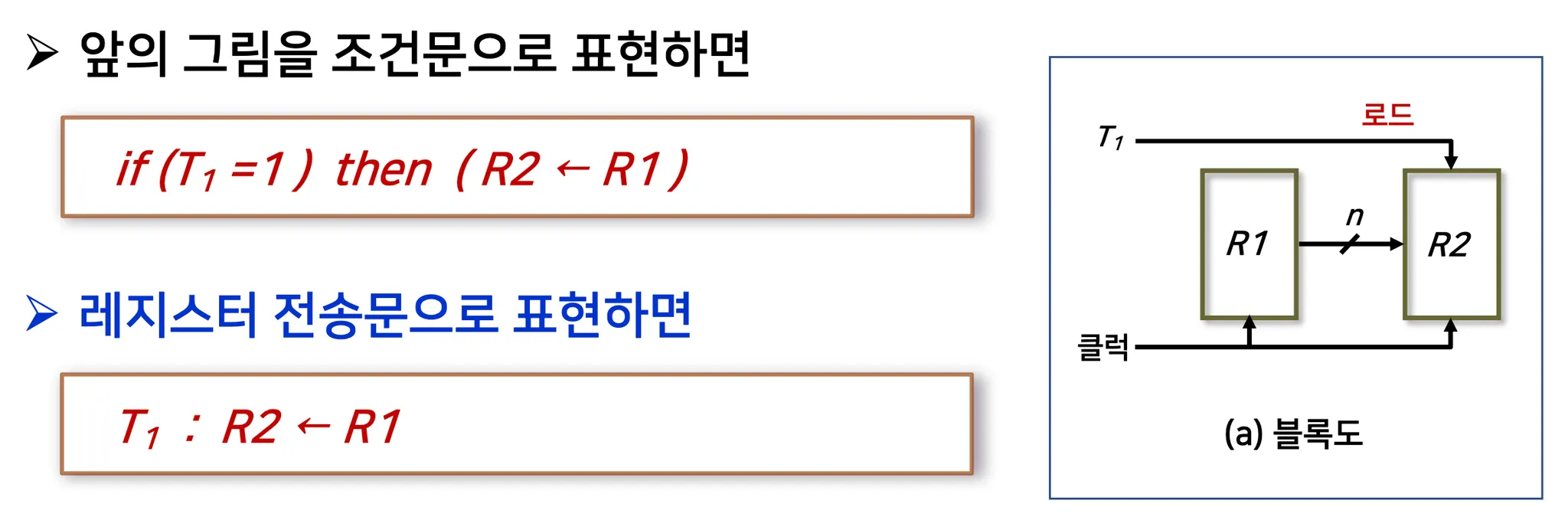

2.4. 논리 마이크로 연산

•

논리 마이크로 연산 (logic micro-operation)

•

레지스터 내의 데이터에 대한 비트를 조작하는 연산

•

기본적인 논리연산으로는 AND, OR, XOR, NOT연산이 있음

2.5. 시프트 마이크로 연산

•

시프트 마이크로 연산 (shift micro-operation)

•

레지스터 내의 데이터를 시프트(shift) 시키는 연산

•

데이터의 측면 이동에 사용

•

시프트 연산을 수행 하더라도 R2 의 값은 변하지 않는다.

•

sr 이나 sl 에대해서 입력 비트는 0으로 가정한다.

•

출력 비트의 값은 버려진다.

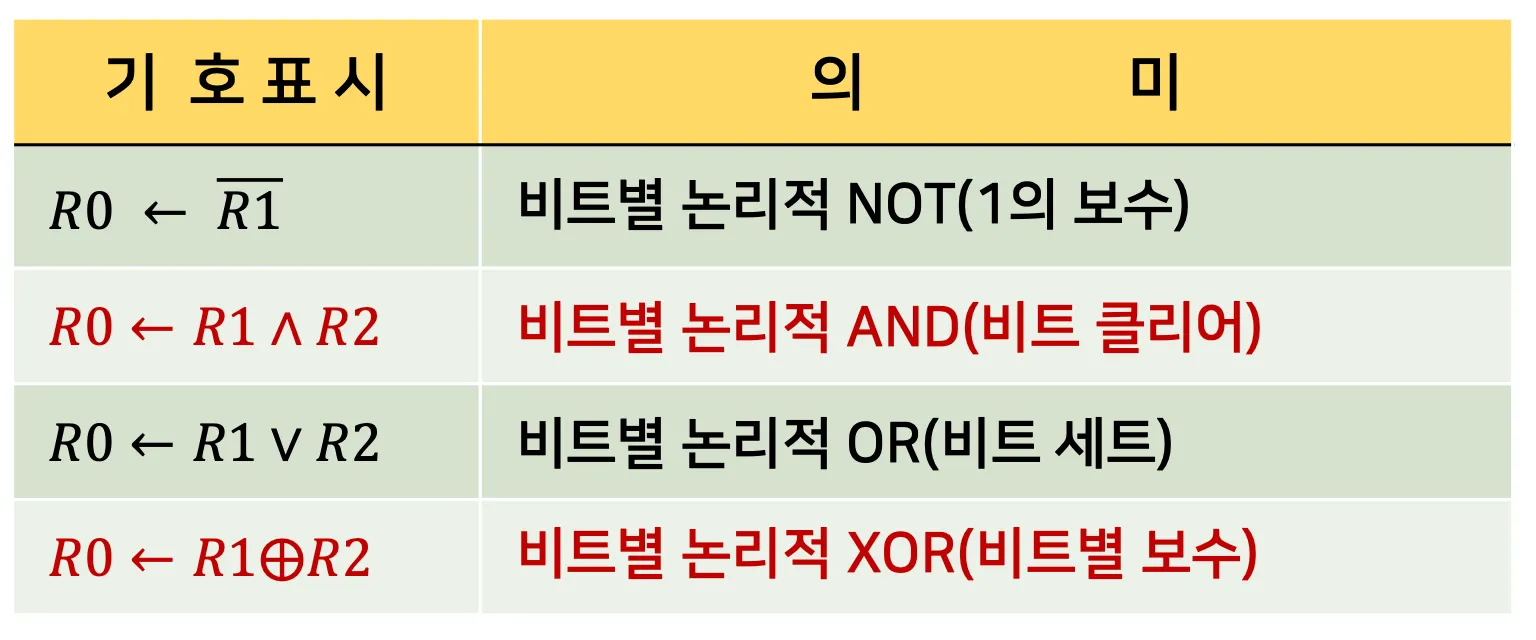

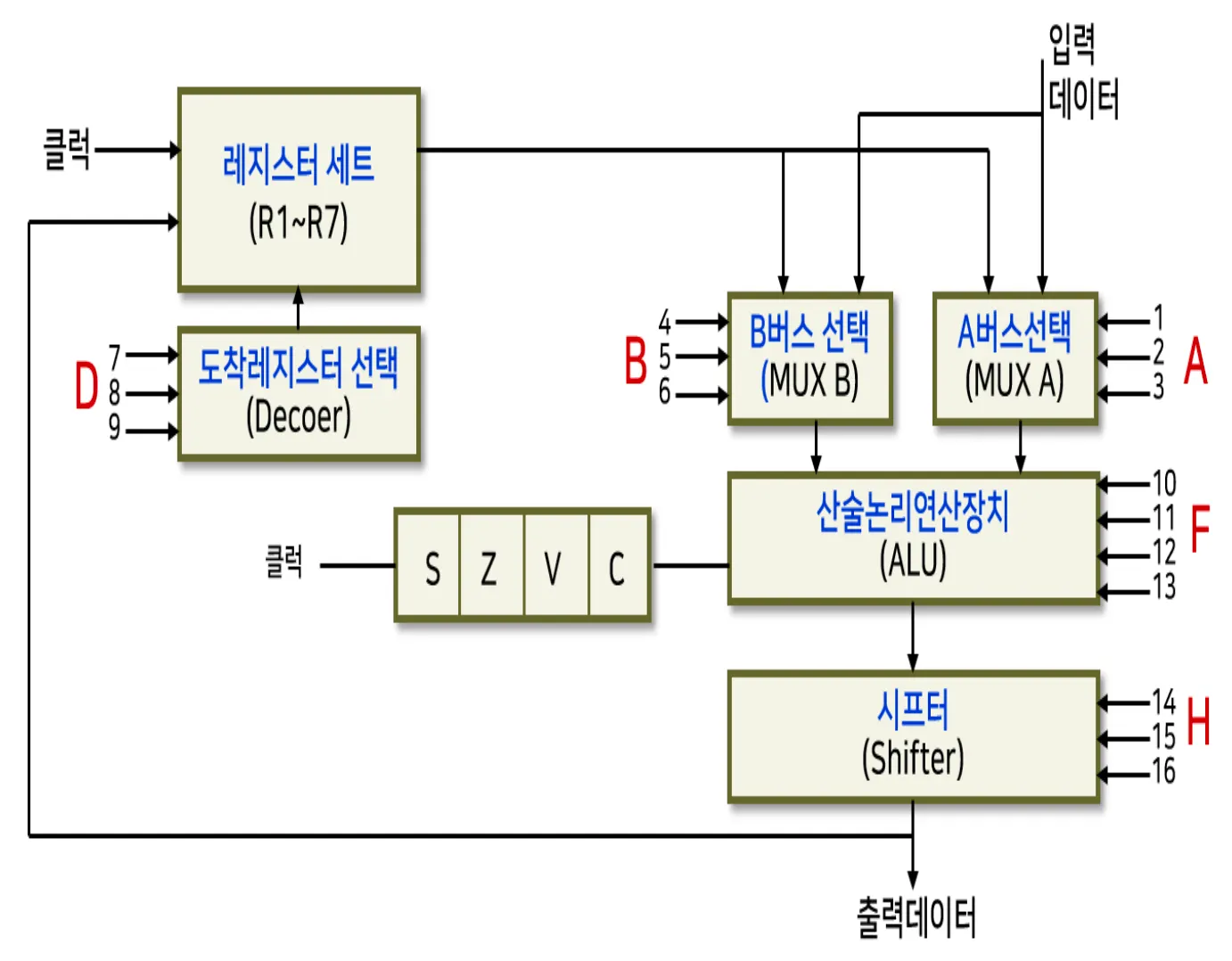

3. 처리장치의 구성요소

•

구성요소

◦

여러개의 레지스터 (레지스터 세트)

◦

산술논리연산장치 (ALU)

◦

내부 버스 (internal bus)

•

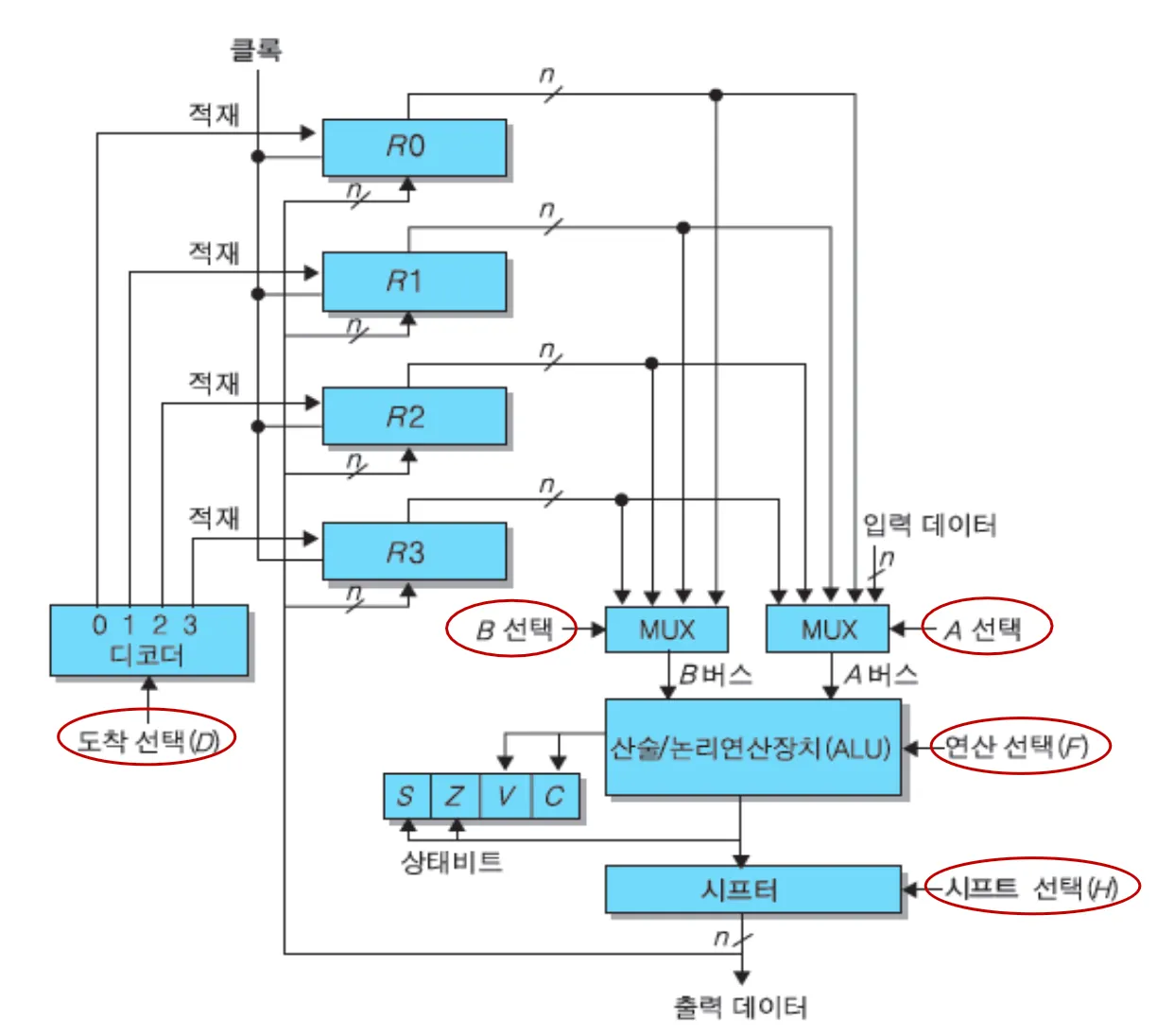

간단한 처리장치의 내부 구성도

3.1. 처리장치에서 마이크로 연산의 수행 과정

•

처리장치의 동작

◦

마이크로 연산의 수행과정을 통해 처리장치가 동작

•

마이크로 연산의 수행 과정

1.

지정된 출발 레지스터의 내용이 ALU의 입력으로 전달

2.

ALU에서 그 연산을 실행

3.

그 결과가 도착 레지스터에 전송

•

처리장치에서 마이크로 연산의 수행 과정

◦

처리장치의 구성요소들의 선택신호에 의해 제어됨

◦

예) R0 ← R1 + R2

1.

선택신호 A는 R1의 내용을 버스 A로 적재

2.

선택신호 B는 R2의 내용을 버스 B로 적재

3.

선택신호 F는 ALU에서 산술연산 A+B를 수행

4.

선택신호 H는 시프터에서 시프트 연산을 수행

5.

선택신호 D는 연산 결과를 R0로 적재

4. 처리장치 구성요소 (1) - 내부 버스

•

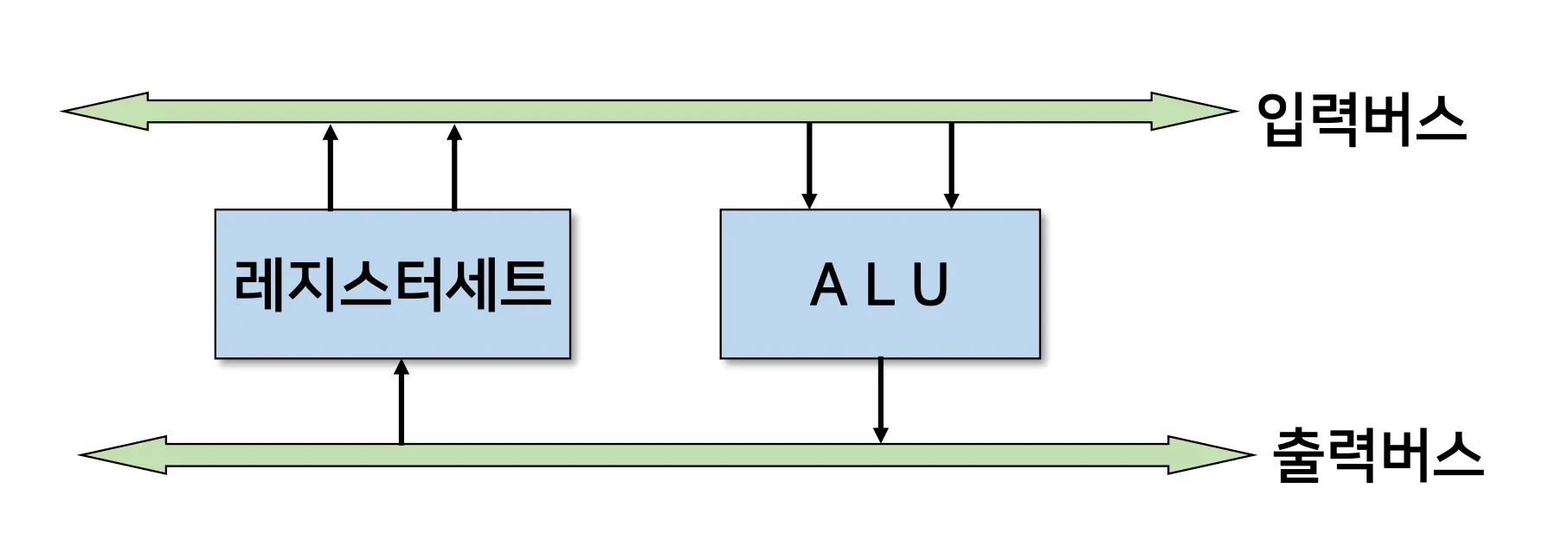

내부 버스

◦

레지스터들 간의 데이터 전송을 위한 공통선로의 집합

•

내부 버스의 개념도

•

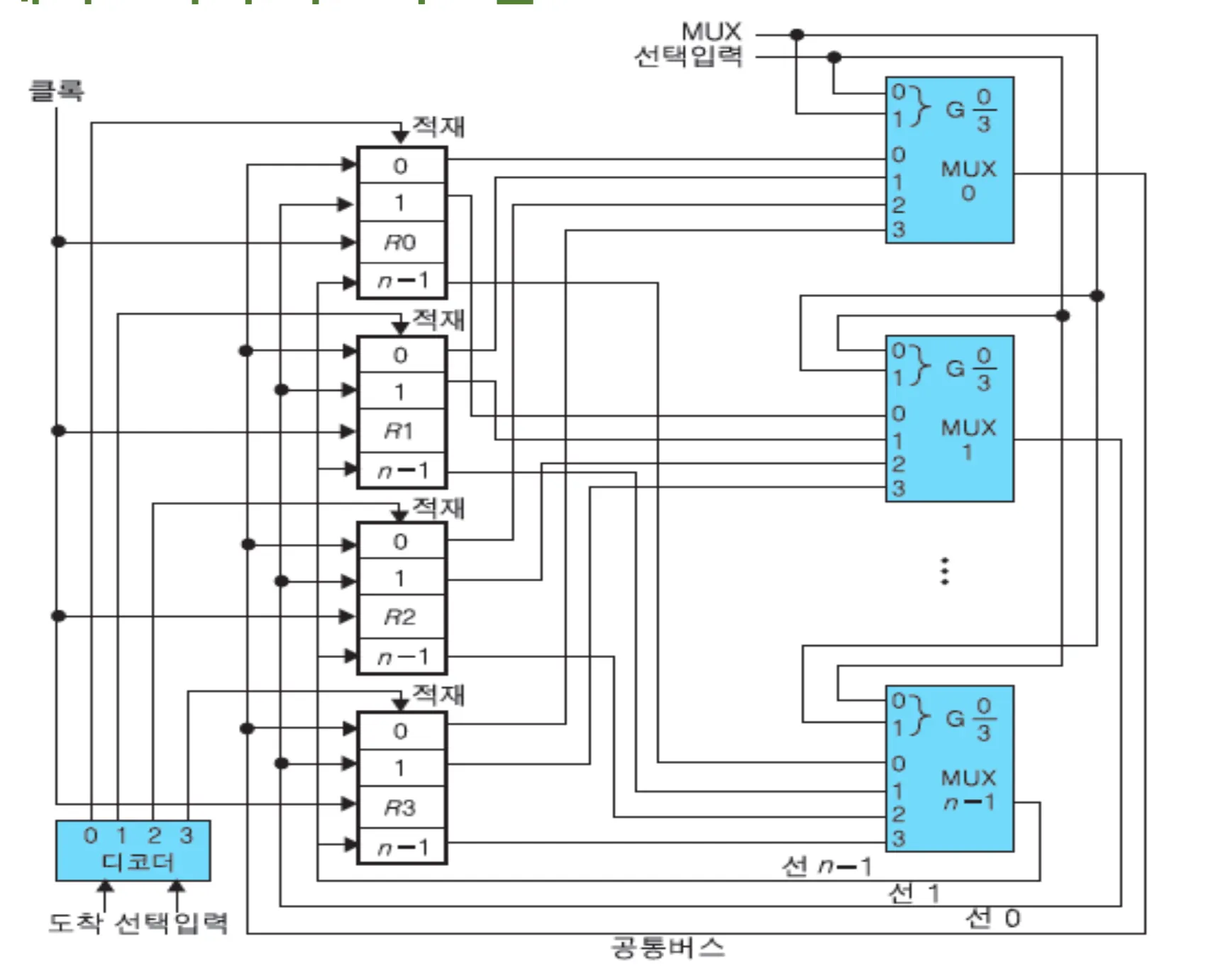

내부 버스를 구성하는 방법

◦

멀티플렉서와 디코더를 이용

◦

멀티플렉서 - 출발 레지스터 선택

◦

디코더 - 도착 레지스터 선택

•

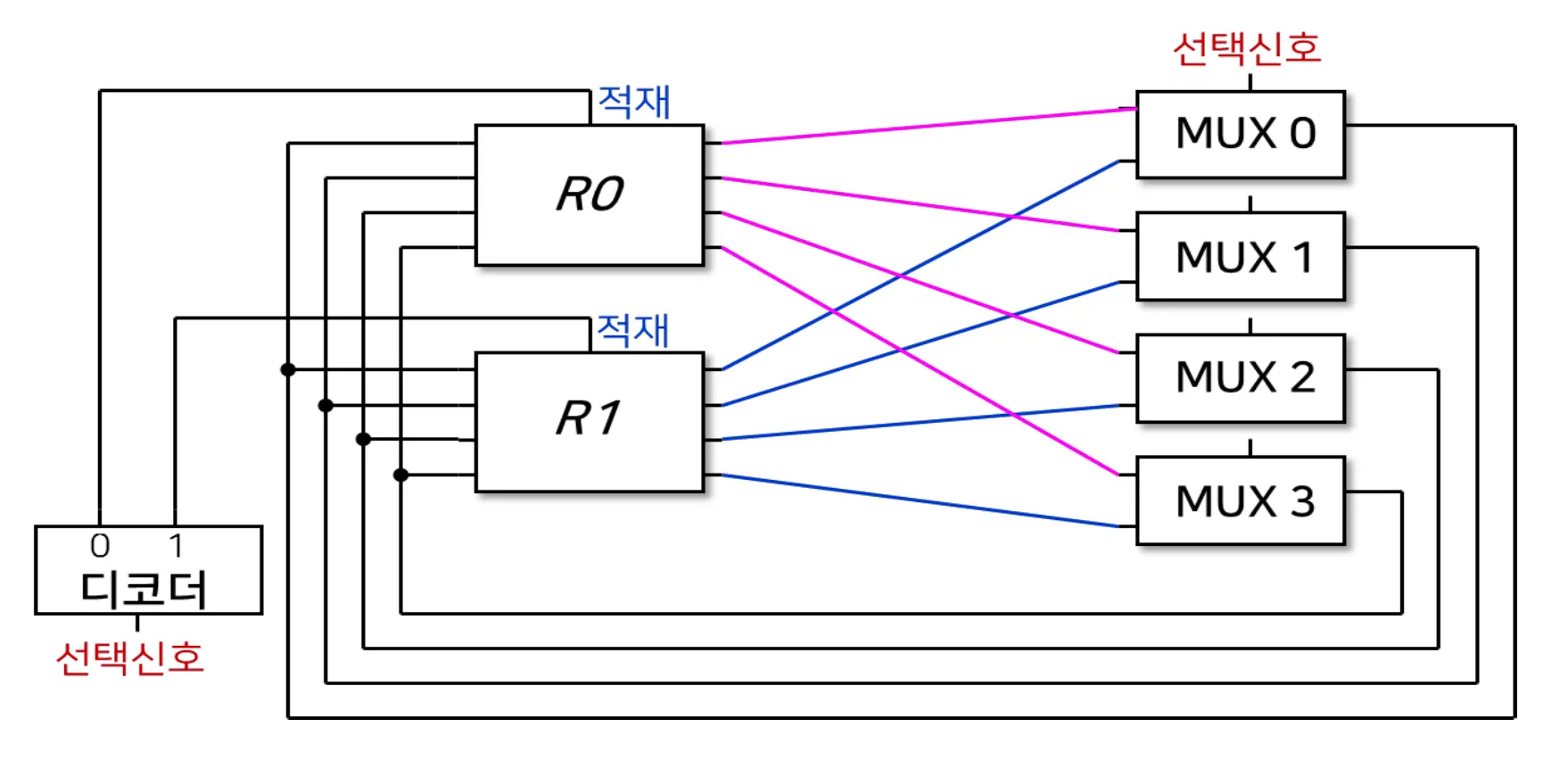

네 레지스터의 버스시스템

•

간단한 내부버스의 구성 및 동작 예시

◦

마이크로 연산: R1 ← R9

◦

R0,R1 이 4비트 레지스터 인 경우

▪

내부버스 구성을 위해 2×1 MUX 4개, 1×2 디코더 1개필요

▪

마이크로 연산을위해 MUX의 선택 신호는 0(2진수), 디코더의 선택 신호는 1(2진수)부여

5. 처리장치 구성요소 (2) - 내부 버스산술논리연산장치(ALU)

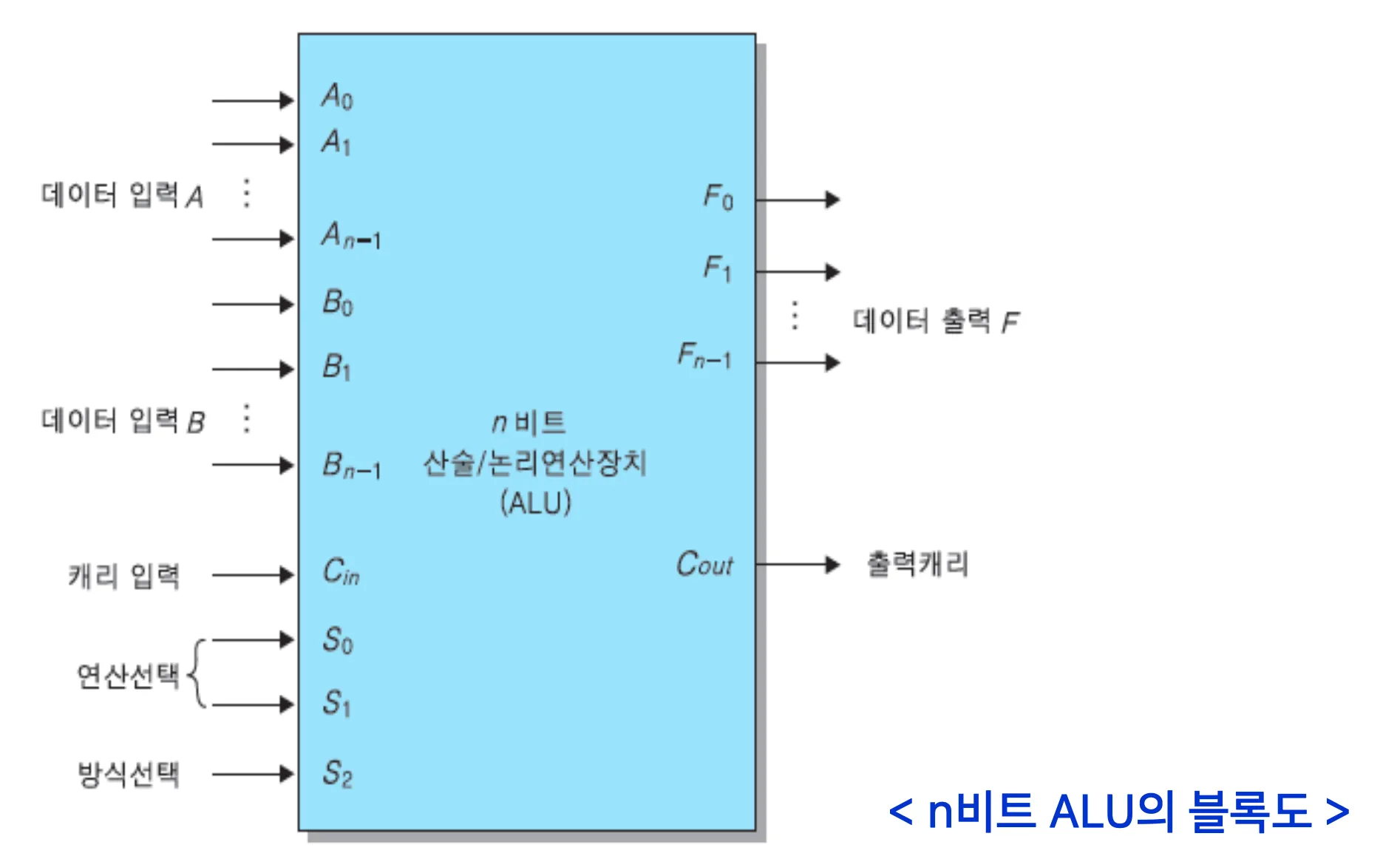

5.1. 산술논리연산장치

•

산술연산과 논리연산을 실행하는 조합논리회로

◦

산술연산회로와 논리연산회로의 결합

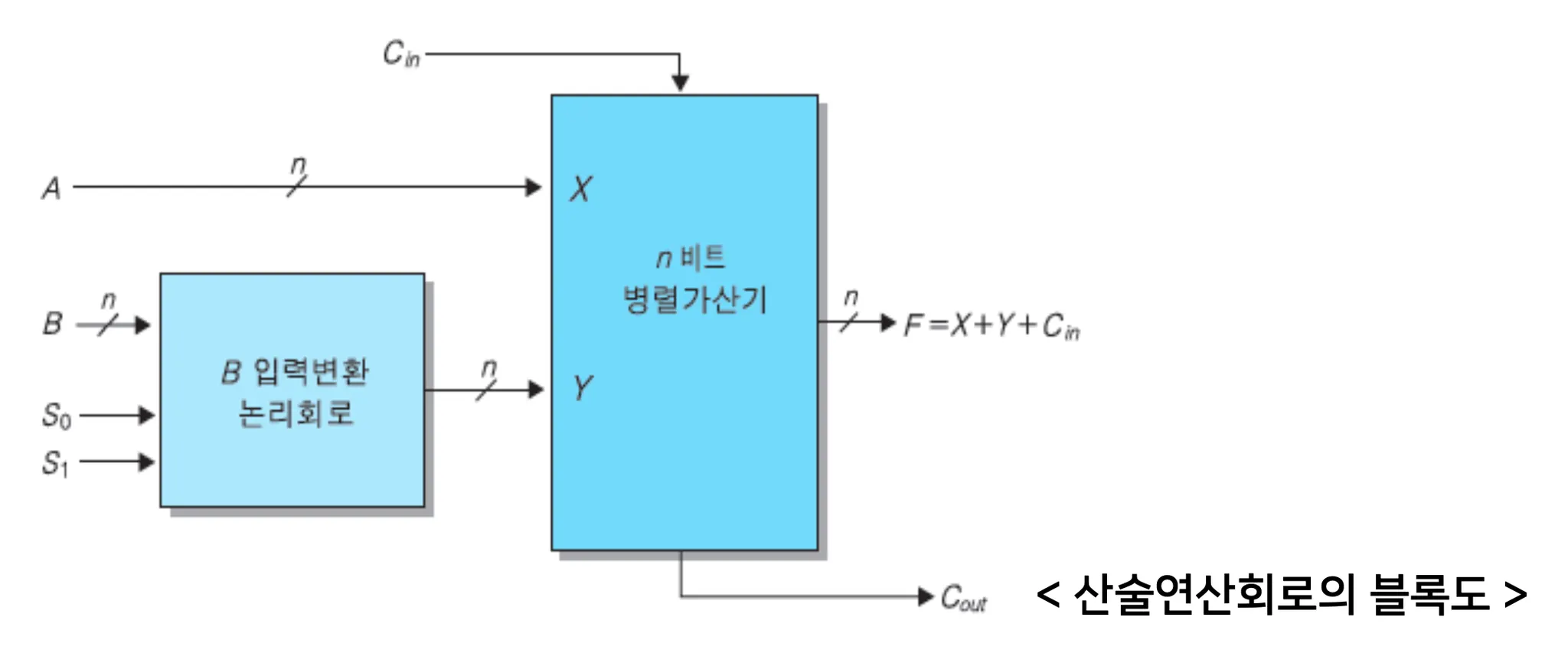

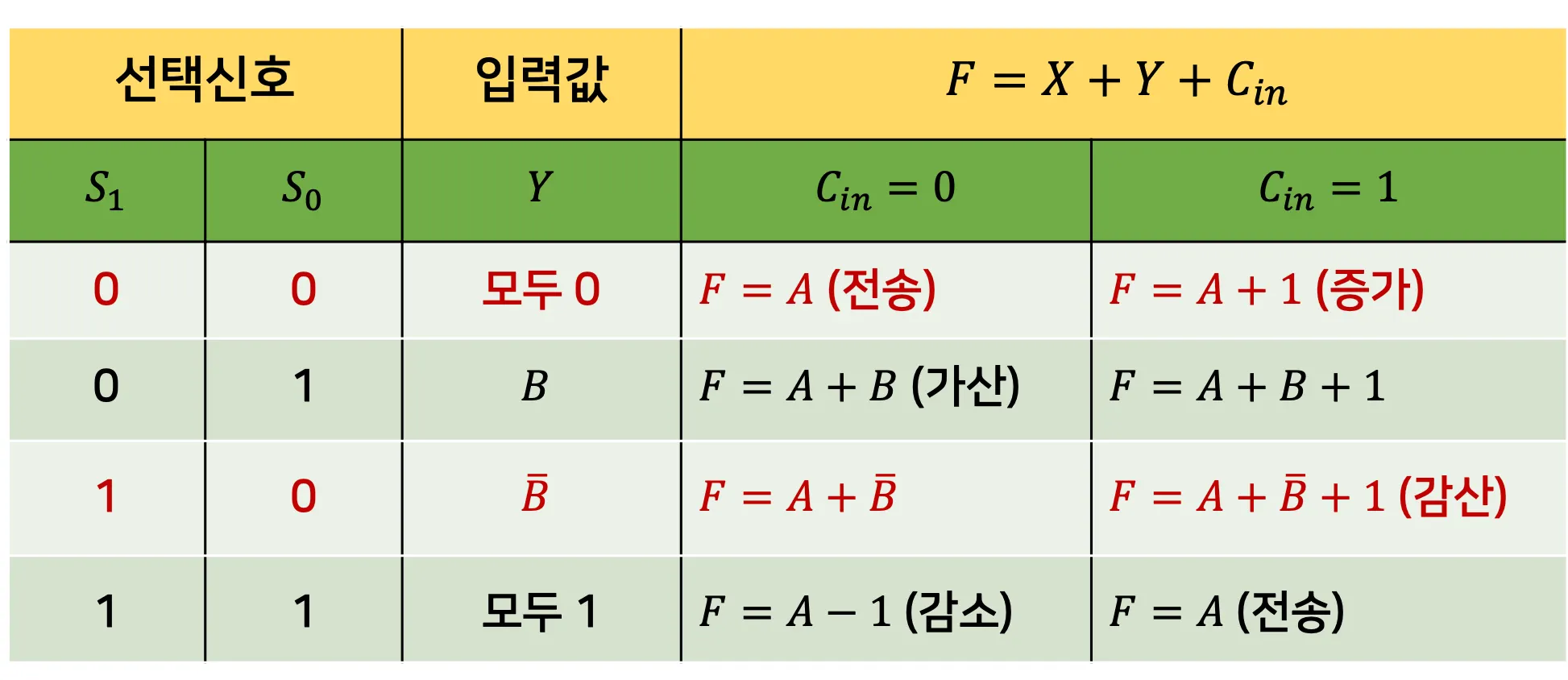

5.2. 산술연산회로

•

여러 개의 전가산기(FA)를 연속적으로 연결한 병렬가산기로 구성

•

병렬가산기로 들어가는 제어입력 값을 선택하여 여러 가지 형태의 산술연산을 실행

•

산술연산의 종류

◦

예)

▪

A + B 덧셈 가산

•

선택비트 010

•

산술연산회로로 옮겨질수 있는 선택비트가 0일경우 → 0010 4비트 선택신호 필요

▪

산술연산회로 경우의 수 8가지, 논리연산회로 경우의 수 4가지 → 12가지 연산 수행 가능

•

입력으로 들어오는 A,B 2개에 있어 각종 연산을 수행하려면 (12가지 중 1개), ALU에서의 선택비트는 4비트가 있어야함

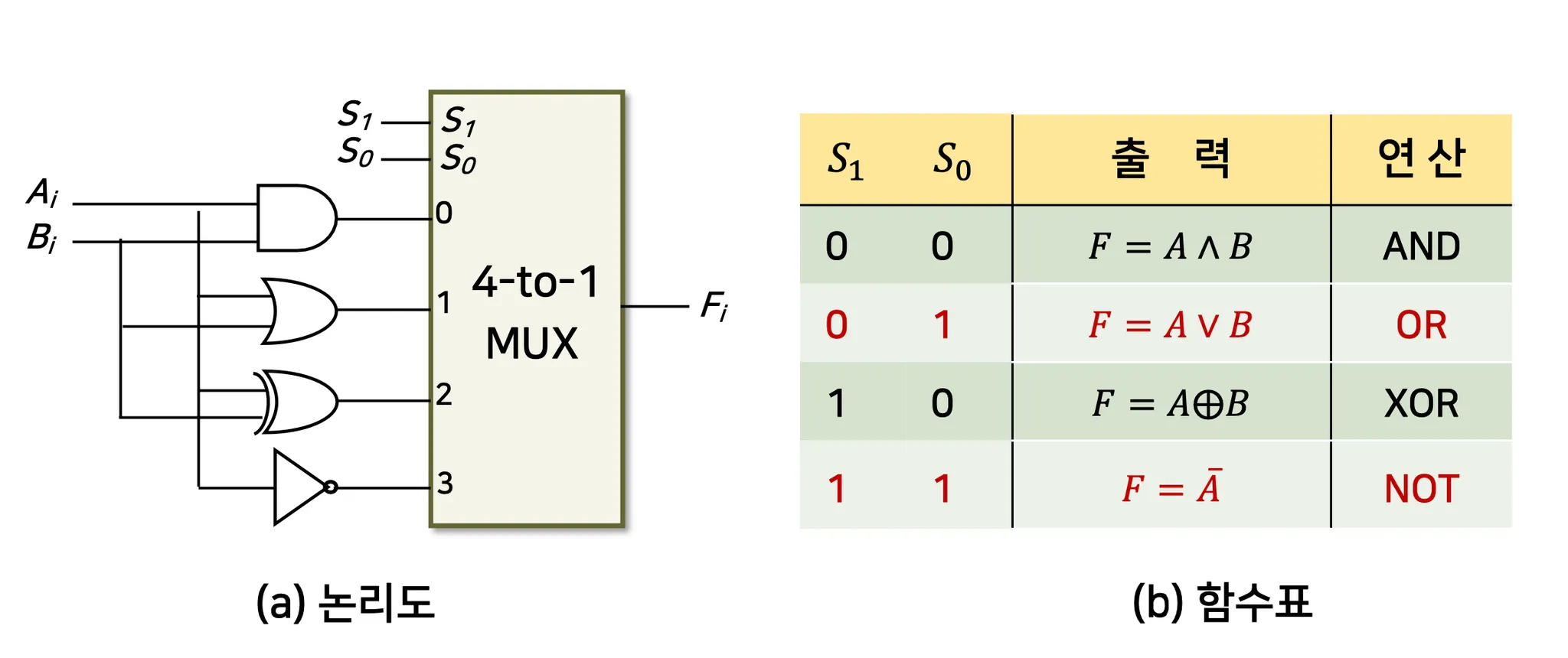

5.3. 논리연산회로

•

레지스터에 있는 각 비트를 독립된 2진 변수로 간주하여 비트별 연산을 실행

•

AND, OR, XOR, NOT 연산 등이 있으며, 이를 이용하여 복잡한 연산을 유도

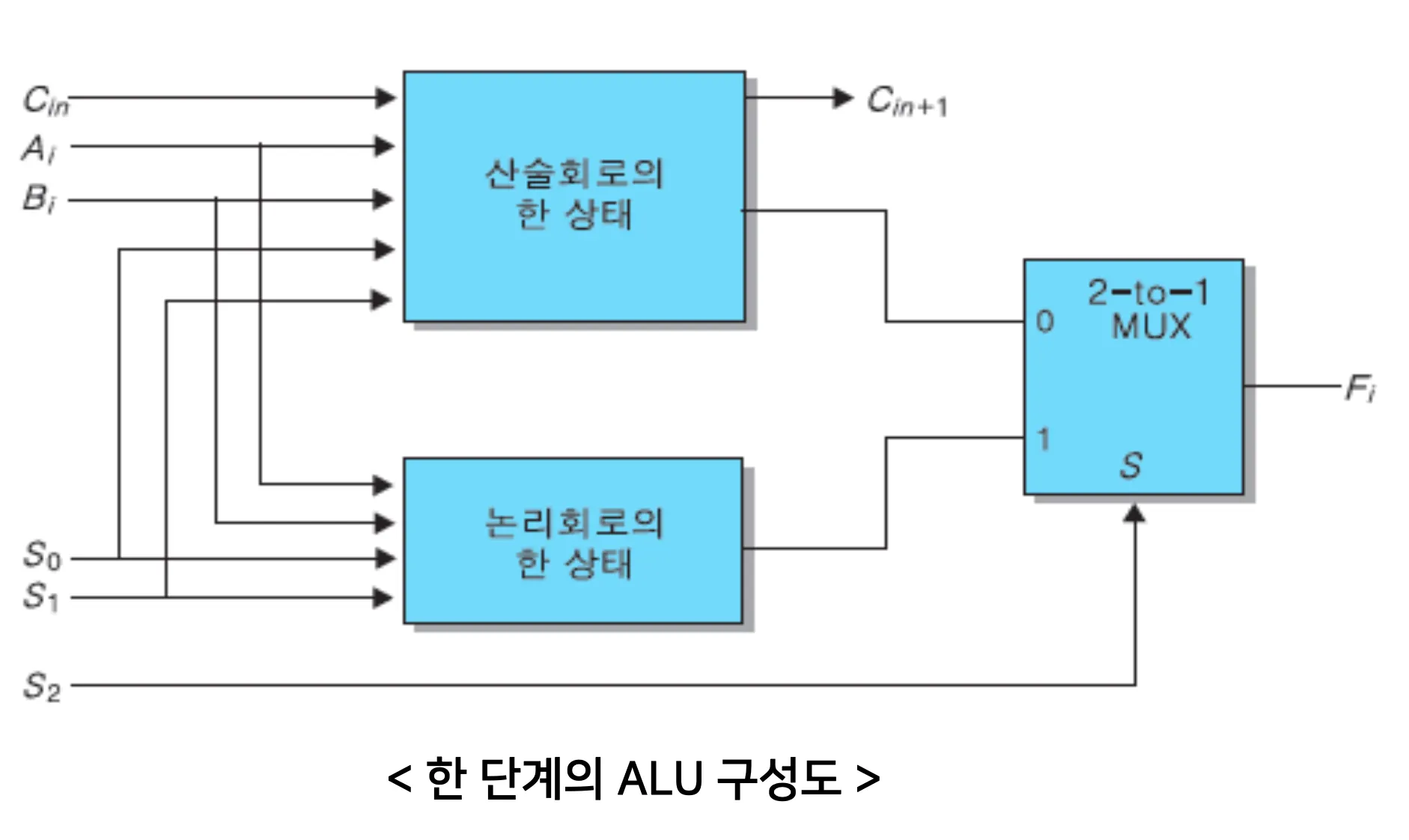

5.4. 산술논리연산회로

•

산술연산장치와 논리연산장치를 결합

•

ALU에 대한 연산표

◦

선택신호의 비트 수는 산술논리연산장치의 연산 종류의 수와 연관됨

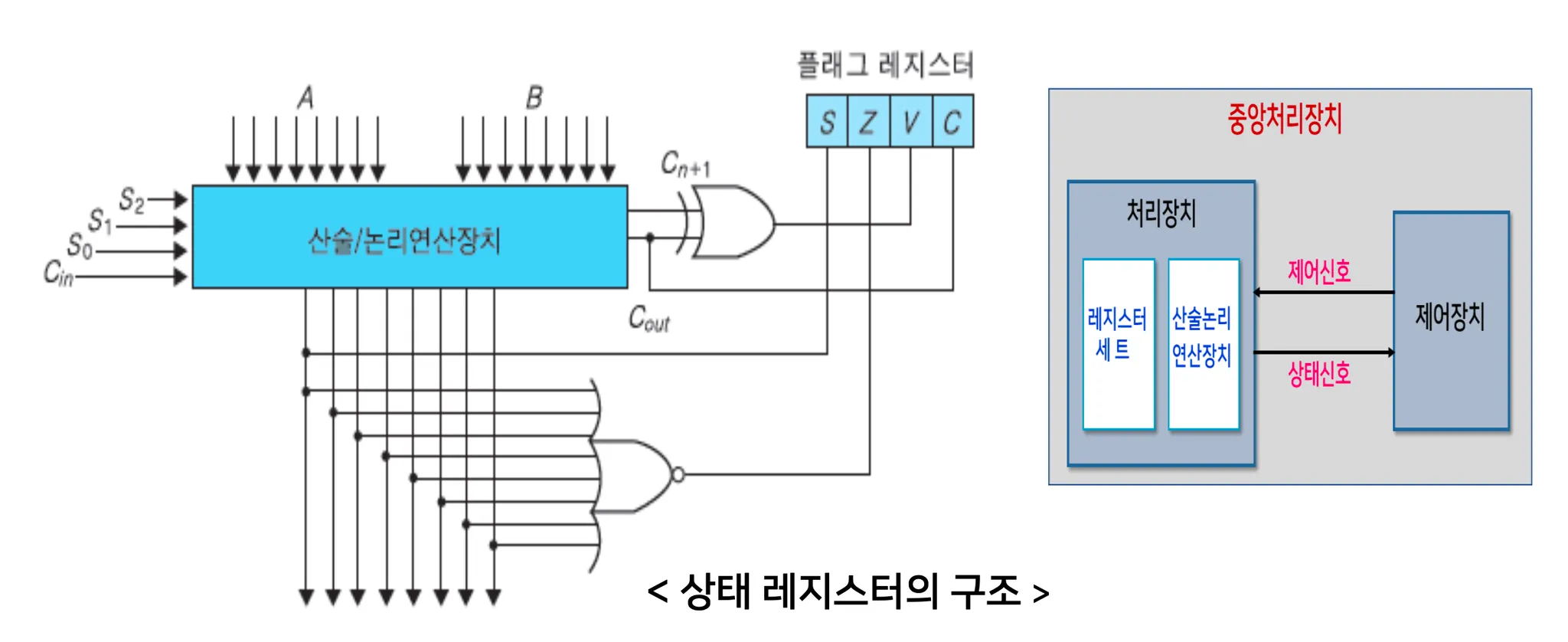

6. 처리장치 구성요소 (3) - 상태 레지스터(flag register)

•

ALU에서 산술연산이 수행된 후 연산결과에 의해 나타나는 상태 값을 저장

•

상태 레지스터의 구성

◦

C(carry bit) - 캐리 발생 유무

◦

S(sign bit) - 부호 변화 발생 유무

◦

Z(zero bit) - 제로 발생 유무

◦

V(overflow bit) - 오버플로우 발생 유무

•

처리 장치 → 제어 장치로 보내는 상태 신호가 상태 레지스터 값을 의미

•

예) 10 - 5 연산 수행

◦

10 + (5의 2의 보수)

▪

10 = 1010

▪

5의 2의 보수 → 0101 → 1010 → 1011

▪

1010 + 1011 → 10101

▪

1의 캐리 발생 → 상태 변화 → 제어할 때 필요 → 보관 필요 → 상태 레지스터에 보관

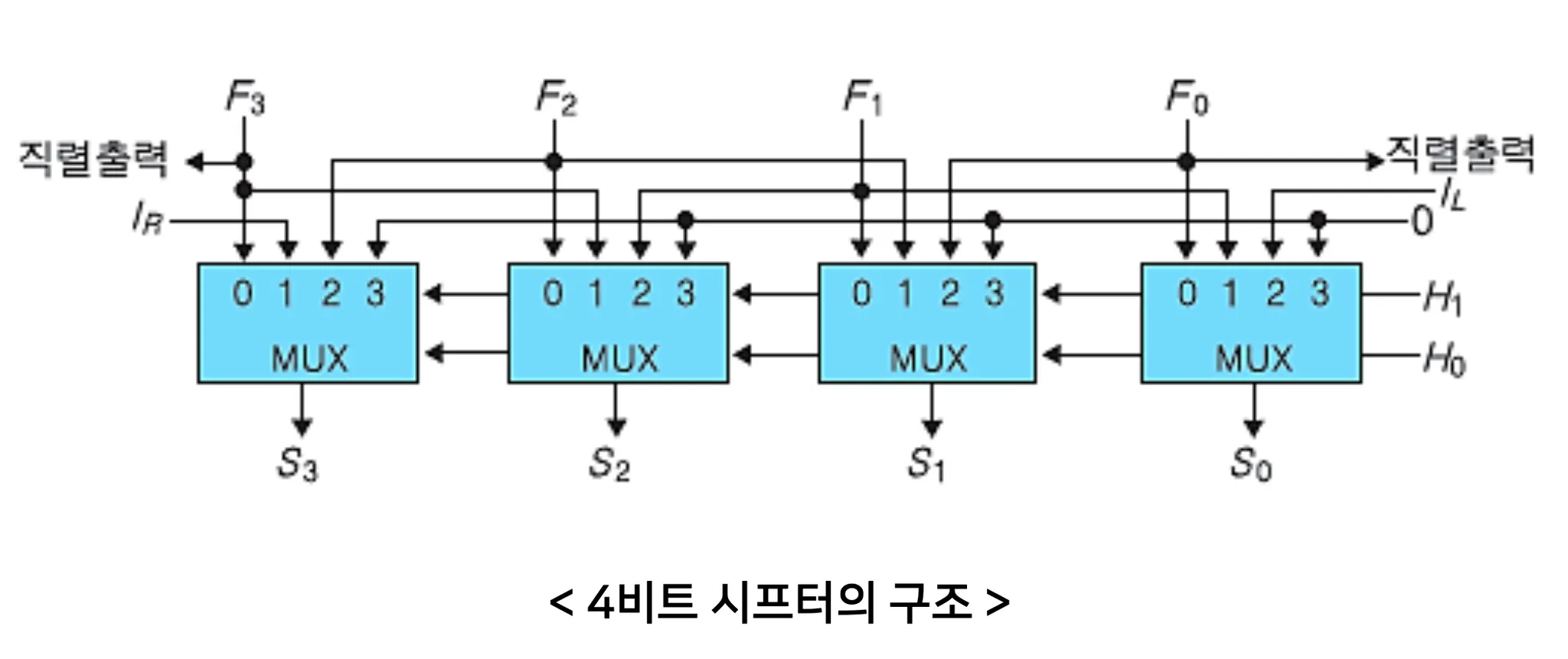

7. 처리장치 구성요소 (4) - 시프터(shifter)

•

입력 데이터의 모든 비트들을 각각 서로 이웃한 비트로 자리를 옮기는 시프트 연산을 수행

•

비트 단위의 이동 수행

•

시프터 연산의 종류

7. 제어단어

7.1. 제어단어

•

제어단어

◦

제어변수(선택신호)들의 묶음

•

선택신호

◦

처리장치내에서 수행되는 마이크로 연산을 선택하는 변수

◦

처리장치의 버스, ALU, 시프터, 도착 레지스터 등을 제어

◦

선택신호 즉 제어변수가 특정한 마이크로 연산을 선택

◦

이러한 제어변수들의 묶음을 제어단어 라고 함

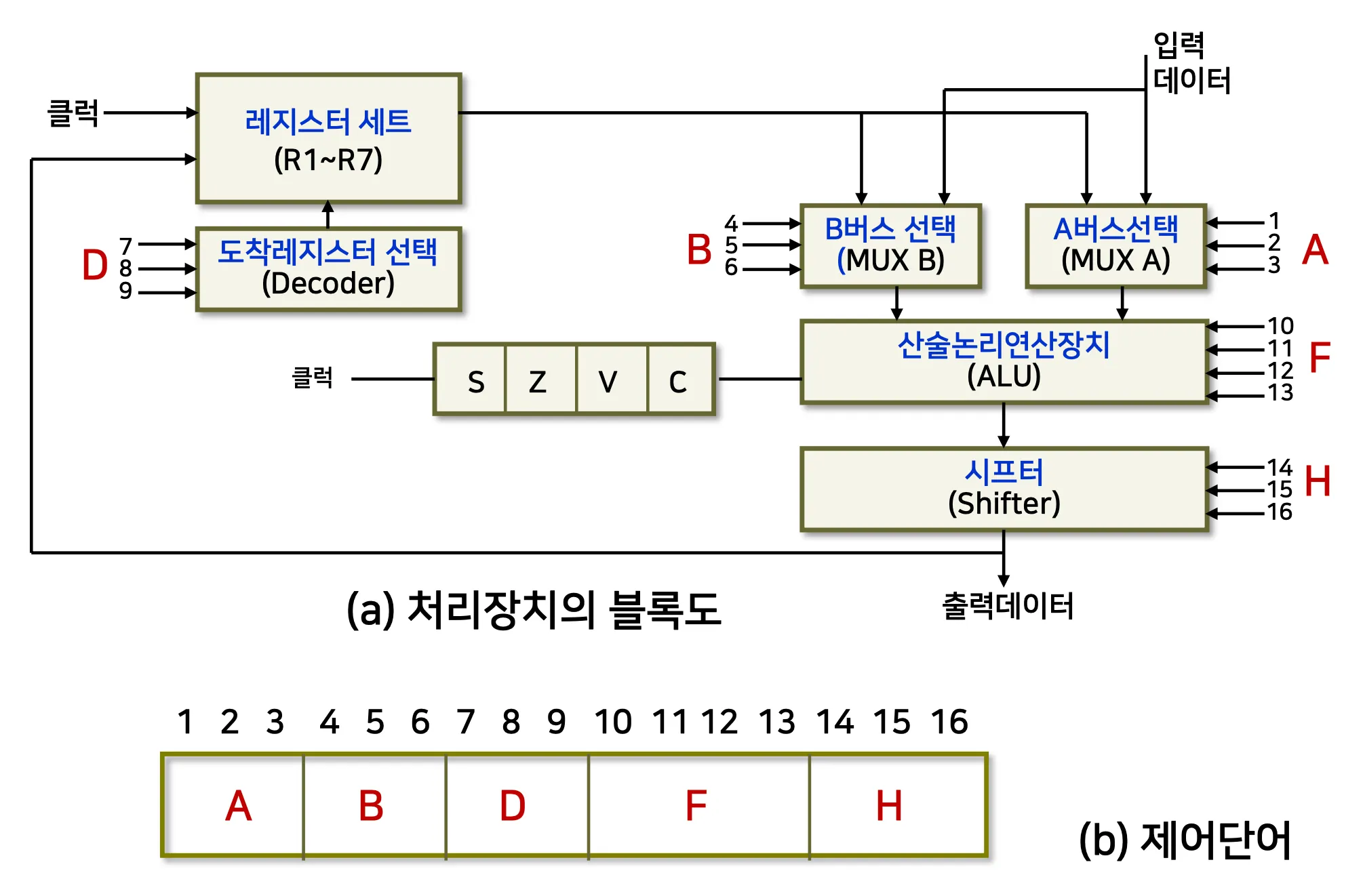

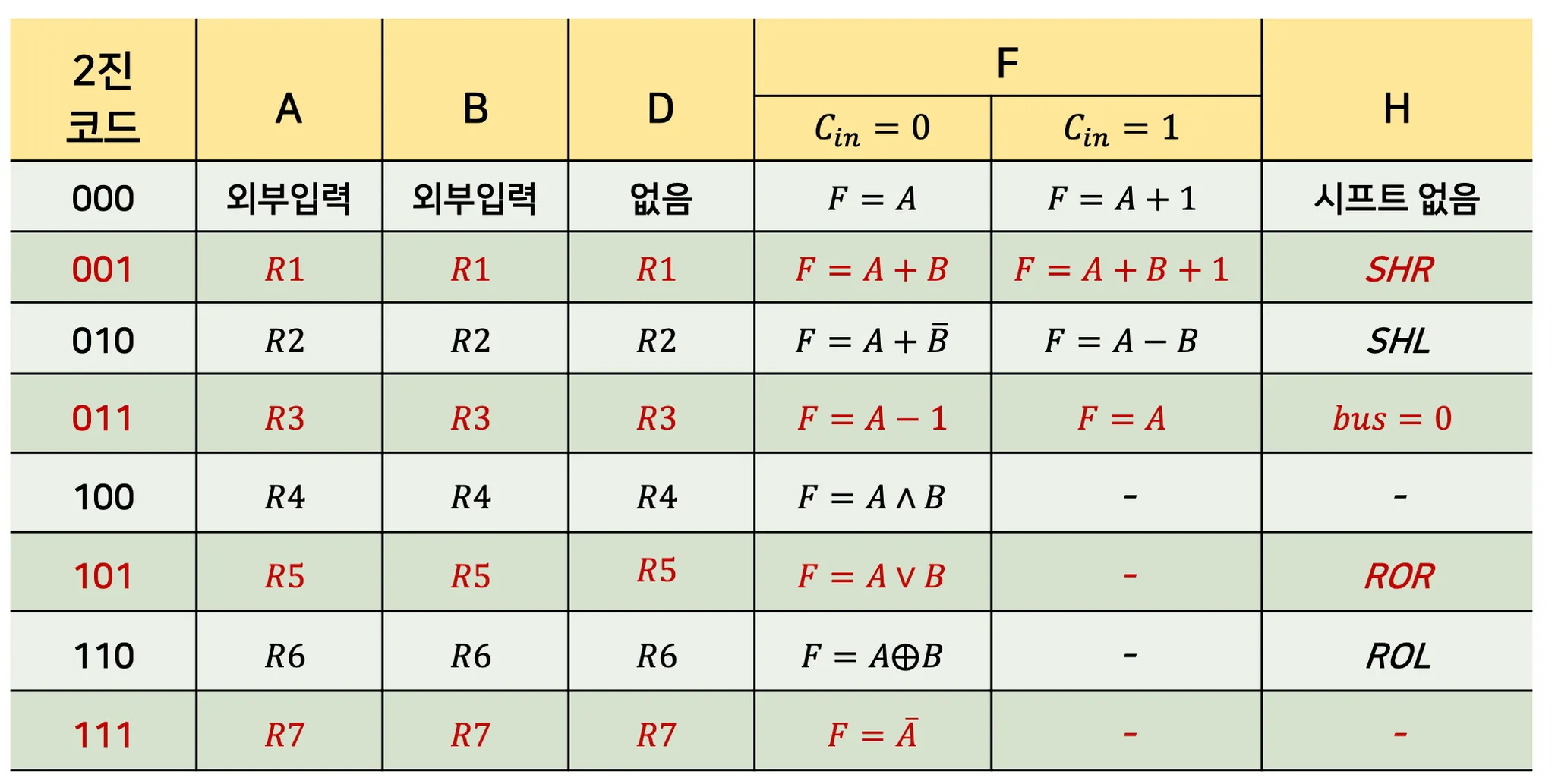

7.2. 제어단어의 내역

•

예를 들어 처리장치의 구성이 다음과 같다면

◦

레지스터 세트: 7개의 레지스터(R1 ~ R7)

◦

산술논리연산장치: 12가지 연산을 수행

◦

시프터: 6가지 연산을 수행

•

처리장치의 구조에서 선택신호와 제어단어의 구성

•

각 필드

◦

A필드: ALU로 입력되는 A버스 선택(3비트)

▪

내부 레지스터 (7개)에서 입력데이터가 들어올 수도 있고, 외부 기억장치 (1개)에서도 들아올 수 있음

▪

따라서 8개 주소가 필요 → 3비트 선택신호 필요

◦

B필드: ALU로 입력되는 B버스 선택(3비트)

▪

위와 동일

◦

D필드: 도착레지스터 선택(3비트)

▪

계산된 결과를 어디에 보낼건지? 내부레지스터 (7개) or 외부 기억장치(1개)

▪

8개의 출력 필요 → 3비트 선택신호 필요

◦

F필드: ALU의 연산 선택(4비트)

▪

12개의 연산 → 4비트 선택 신호 필요

◦

H필드: 시프터의 연산 선택(3비트)

▪

6가지 연산 → 3비트 선택 신호 필요

7.3. 제어단어 각 필드의 동작

•

A와 B 필드의 3비트

◦

ALU로 입력되는 각각의 출발 레지스터를 선택

•

D필드의 3비트

◦

ALU의 결과가 저장될 도착 레지스터를 선택

•

F필드의 4비트

◦

ALU에서 이루어지는 12가지 연산 중 하나를 선택

•

H필드의 3비트

◦

시프터에서의 시프트 연산중 하나를선택

→ 전체 16비트로 구성된 선택신호들의 모임(제어단어)을 처리장치의 각 구성요소에 가하면 해당 마이크로 연산이 수행됨

7.3. 제어단어의 내역표

•

제어단어의 내역표 예시

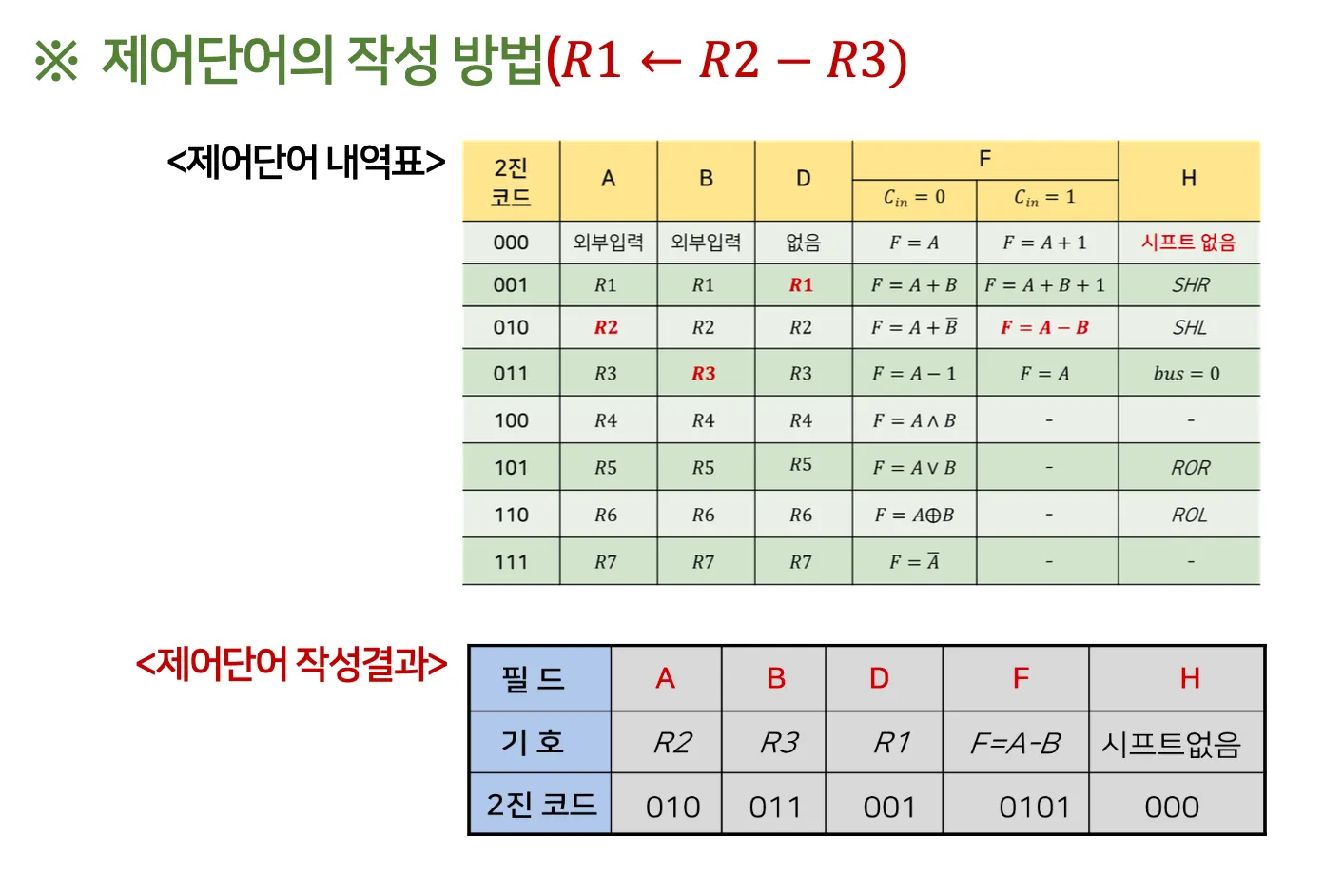

7.4. 제어단어 작성 예

•

R1 ← R2 − R3

•

A 필드 : ALU의 A 버스 입력으로 R2 의 내용을 보낸다.

•

B 필드 : ALU의 B 버스 입력으로 R3 의 내용을 보낸다.

•

D 필드 : 연산 결과를 도착 레지스터 R1으로 보낸다.

•

F 필드 : ALU에서 감산 연산 (F=A-B)을 수행한다.

•

H 필드 : 시프터에서 연산을 수행하지 않는다.(시프트 없음)

•

여러 가지 마이크로 연산에 대한 제어단어의 예

7.5. 제어단어 생성을 위한 효과적인 방법

•

작성된 제어단어를 기억장치에 저장하고 기억장치의 출력을 처리장치의 각 구성요소의 선택신호로 연결

•

기억장치로부터 연속적인 제어단어를 읽음으로써 처리장치에서의 마이크로 연산이 정해진 순서대로, 연속적으로 수행

→ 제어장치의 역할